When I first started dabbling in digital logic design, I felt like I was hitting a brick wall made of expensive, proprietary software. If you have ever tried to download a professional FPGA design suite, you know exactly what I am talking about. You have to sign up for accounts, wait for license keys, and then download fifty gigabytes of data just to blink an LED on a small piece of hardware. This is why discovering Yosys was such a game-changer for me. It felt like the first time I moved from Windows to Linux. Suddenly, the “black box” of hardware synthesis was cracked wide open, and I could actually see, touch, and modify the gears turning inside the machine.

Yosys, which stands for Yosys Open Synthesis Suite, is essentially the heart of the open-source hardware movement. At its most basic level, it is a tool that takes your high-level Verilog code and translates it into a netlist, which is a giant map of gates and wires that a chip can actually understand. But calling it just a translator is doing it a massive disservice. It is a modular, extensible framework that has allowed developers to build entire ecosystems for FPGA and ASIC design without ever needing to ask permission from a corporate giant. It represents a shift in philosophy where the tools we use to build our world are owned by the community rather than held behind a paywall.

To understand why Yosys is so special, we have to look at the synthesis process itself. When you write code in Verilog, you are describing how data should flow through a system. However, a piece of silicon does not understand “if-then” statements or “always” blocks. It understands transistors and physical connections. Yosys acts as the bridge. It starts by reading your Verilog files and converting them into an internal format called RTLIL, or RTL Intermediate Language. This is a crucial step because it allows Yosys to perform “passes” on the design. Think of these passes like filters in a photo editor. One pass might look for unused logic and delete it, while another might look for ways to share a single piece of hardware between two different operations to save space.

One of the most impressive parts of the Yosys architecture is how it handles logic optimization. For this, it often reaches out to an external tool called ABC, which was developed at Berkeley. ABC is world-class software for logic minimization. When Yosys hands off a design to ABC, the tool looks at the massive web of Boolean logic and tries to find the mathematically simplest way to represent it. This is not just about being tidy. In the world of hardware, fewer gates mean less power consumption and less heat. It also means your design can run at a higher clock speed because the signals have less distance to travel through the gates. Seeing this collaboration between different open-source projects is one of the most beautiful aspects of the ecosystem.

For a long time, the biggest criticism of open-source hardware tools was that they did not support “real” hardware. That changed forever with Project IceStorm. A group of brilliant hackers managed to reverse-engineer the bitstream format of the Lattice iCE40 FPGA, and Yosys was the tool that made it possible to actually synthesize code for it. I remember the excitement in the community when we realized we could finally have a 100% open-source toolchain from top to bottom. You could write code in a text editor, synthesize it with Yosys, place and route it with Nextpnr, and upload it to the board with Iceprog. No licenses, no massive installers, just pure engineering freedom. Since then, support has expanded to the Lattice ECP5, and we are even seeing experimental support for parts of the Xilinx and Gowin ecosystems.

The flexibility of Yosys is also what makes it a powerhouse for formal verification. Most beginners think that testing hardware means running a simulation and looking at waveforms on a screen. While that is useful, it is also prone to human error because you can only test the scenarios you can think of. Formal verification, using a tool called SymbiYosys which is powered by Yosys, takes a different approach. It uses mathematical solvers to prove that your design will never enter a bad state, no matter what inputs it receives. This is the kind of stuff they use to design chips for satellites and medical devices. Because Yosys is open and scriptable, it makes this high-level verification accessible to hobbyists and small startups who could never afford the six-figure price tags of commercial formal tools.

If you are coming from a background of using GUI-heavy tools like Vivado or Quartus, the Yosys command line might feel intimidating at first. However, once you get used to it, you will never want to go back. Yosys uses a TCL-based scripting interface, which means you can automate everything. You can write a simple script that synthesizes your design, runs optimizations, and generates a report on gate usage in seconds. This is a massive boon for Continuous Integration (CI) pipelines. Imagine a scenario where every time you push code to GitHub, a server automatically runs Yosys to make sure your design still fits on the chip and meets timing requirements. This level of automation is difficult and clunky with proprietary tools, but it is the default way of working with Yosys.

Another thing I love about Yosys is the community and the organization behind it, YosysHQ. They have managed to bridge the gap between hobbyist “hackers” and professional industrial users. They provide commercial support for companies that want to use these tools in production, which gives the project a level of stability and longevity that many open-source projects lack. This “pro” side of the ecosystem ensures that bugs are fixed quickly and that new features, like support for SystemVerilog or VHDL via plugins, are constantly being developed. It is a perfect example of how open source can be both a labor of love and a viable professional tool.

We should also talk about the role Yosys plays in the ASIC world. For decades, designing your own custom silicon chip was a dream that only massive corporations could afford. But with projects like OpenLane and the Google-sponsored SkyWater 130nm PDK, the barriers are falling. Yosys is the synthesis engine under the hood of these ASIC flows. It takes the RTL and maps it to specific standard cells provided by the foundry. This is a monumental shift. We are entering an era where an independent designer can sit at a laptop, use Yosys to synthesize a CPU, and actually get physical chips back in the mail a few months later. None of this would be possible without a robust, open-source synthesis engine.

Of course, no tool is perfect. Yosys still has some hurdles to clear when it comes to full SystemVerilog support, although the integration with Verilator and specialized front-ends is rapidly closing that gap. Also, if you are working on the absolute latest, high-end FPGAs from Xilinx or Intel, Yosys might not be able to utilize every single proprietary hard-IP block as efficiently as the vendor’s own tools. But for 90% of use cases, and especially for education and small-to-medium scale production, Yosys is more than capable. In fact, its transparency often makes it easier to debug why a circuit is failing compared to the opaque error messages you get from proprietary software.

When you use Yosys, you are not just using a tool, you are participating in a movement to democratize hardware. You are learning the actual science of logic synthesis rather than just learning which buttons to click in a specific vendor’s interface. This knowledge is portable. The concepts of technology mapping, gate-level netlists, and logic optimization are universal. By stripping away the shiny, distracting interface, Yosys forces you to become a better hardware engineer. You start to think about how your code translates into physical hardware, and that awareness leads to more efficient and reliable designs.

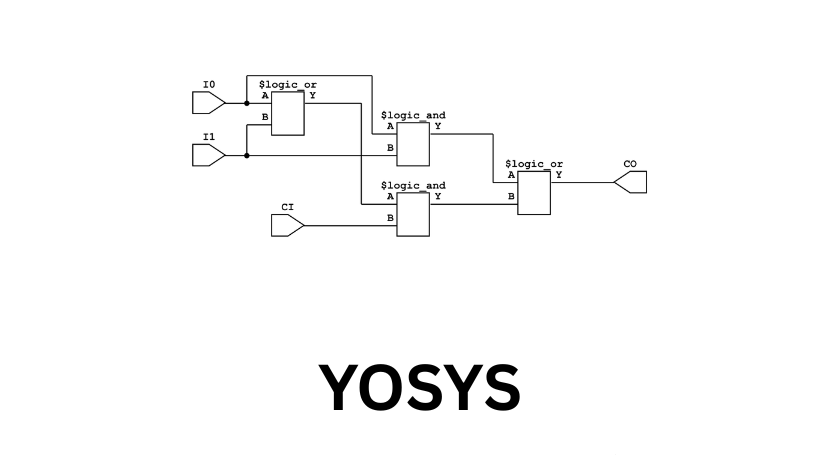

In my own work, I have found that using Yosys has significantly sped up my development cycle. Instead of waiting for a heavy IDE to load, I keep a terminal window open. I make a change to my Verilog, run my Yosys script, and I have results in a heartbeat. It feels snappy and responsive. If I want to see exactly how Yosys interpreted a specific module, I can use the “show” command to generate a visual diagram of the logic. This visual feedback is incredibly helpful for catching stupid mistakes, like accidentally creating a latch or forgetting to connect a signal. It turns the abstract world of code into something tangible and visual.

In conclusion, Yosys is more than just a piece of software. It is the foundation upon which the future of open-source silicon is being built. Whether you are a student learning digital logic for the first time, a hobbyist playing with an iCEstick, or a professional engineer looking to automate your workflow, Yosys offers a level of power and flexibility that proprietary tools simply cannot match. It reminds us that at the end of the day, hardware is just logic, and logic belongs to everyone. By mastering Yosys, you are taking control of your design process and joining a global community of innovators who are proving that the best tools don’t always come with a price tag.

FAQ

Is Yosys better than Xilinx Vivado?

It depends on your goals. Vivado is better for high-end, cutting-edge Xilinx chips and offers more advanced place-and-route for those specific devices. However, Yosys is significantly faster, lightweight, open-source, and superior for automation and formal verification. For supported FPGAs like the iCE40, Yosys is often preferred.

Does Yosys support SystemVerilog?

Yosys has basic support for SystemVerilog, but for complex designs, it is often used with a plugin or a pre-processor like Verific (which is commercial) or through the “systemverilog” plugin which is continuously improving. Many users find it sufficient for most RTL needs.

Can I use Yosys for ASIC design?

Yes, Yosys is a core component of open-source ASIC flows like OpenLane and SiliconCompiler. It can map logic to specific cell libraries provided by semiconductor foundries.

What language is Yosys written in?

Yosys is primarily written in C++, which contributes to its high performance and speed during the synthesis process.

Can Yosys handle VHDL?

Direct VHDL support is not built into the core, but you can use the GHDL plugin for Yosys. This allows you to synthesize VHDL designs by using GHDL as a front-end to read the files and pass them to Yosys.